<del>ؠ</del>ؖڐ

Ð

# JUNE 23-27, 2024

**MOSCONE WEST CENTER** SAN FRANCISCO, CA, USA

**SPONSORED BY**

IN TECHNICAL COOPERATION WITH

$\bigcirc$

ê

**DIAMOND EVENT SPONSOR**

$\mathcal{L}$

# DEAR COLLEAGUES AND FRIENDS,

# Welcome to 61st DAC - the "Chips to Systems Conference"!

DAC turned 60 last year. and we had a major celebration of its rich and long history as being the premier global research conference and industry event in electronic design and design automation. While EDA still remains at the core of DAC, we have seen some expansion in the topics of interest. Besides the traditional topics of EDA design, IP and Embedded Systems, we now have three additional topics -- AI, Autonmous Systems and Security.

The number of submissions in AI – both AI for chip design and AI hardware design and architecture – have literally exploded over the last few years and there seems to be no end in sight. AI is now 13% of the program and growing rapidly. We are embracing this expansion of DAC topic areas. Yes, still EDA at heart – but we're now featuring a much broader set of offerings for researchers and practitioners across industry and academia. As the premier global event for chips to systems, DAC is now very well-positioned to serve the rapidly evolving needs of the design and design automation communities across the world.

DAC61 has four wonderful keynote talks highlighting AI, Systems Foundry and Immersive Computing, along with several exciting SKYtalks and Techtalks covering a range of topics in chips, systems and applications.

There are 337 research papers across 29 tracks. We had a 34% increase in research paper submissions this year across all tracks and from all over the world, and a record 1,545 submissions—this is after an all-time record of submissions set last year. There are several Special Sessions featuring leading-edge research presentations by renowned experts along with Research Panels featuring luminaries from academia and industry discussing hot topics of current interest. To round out the Research Track, there are also Late Breaking Results (LBR) poster presentations and work-in-progress poster sessions.

Adding to the robust Research Track program is the exciting Engineering Track program targeted for industry practitioners and technical managers, focusing on four key areas: front-end design, back-end design, IP and embedded systems and software. Here, engineers from the industry share the latest innovations and key advancements. We had a 32% increase in the number of submissions this year, with strong focus on AI, Design and IP. We also have several invited presentations and panels featuring industry experts and executives discussing the latest hot topics driving innovation.

The exhibition floor is once again a highlight of the event, with the DAC Pavilion featuring analyst presentations, SKYtalks, Techtalks and controversial panels for lively discussions, along with the daily Poster Gladiator competition which is always fun to attend. New this year, the exhibit floor will host the Exhibitor Forum Theater with hourly technical presentations from exhibitors showcasing their technology and methodology offerings. We are pleased to also host 25 new exhibitors at this year's DAC! Make sure to visit the exhibition floor and check out the new technologies on the horizon.

Finally, I want to thank all who have helped to make DAC61 possible: Many thanks to my colleagues from the DAC EC, the TPC members of both the research and the engineering tracks, all the volunteers and employees from the sponsor's societies/councils as well as the management companies.

I look forward to welcoming you in person at the Moscone West in San Francisco – the "most cordial and sociable city", in the words of Mark Twain!

VIVEK DE 61st DAC General Chair

# TABLE OF CONTENTS

| Conference Information                                                    | 04                                     |

|---------------------------------------------------------------------------|----------------------------------------|

| DAC Directory Maps                                                        | 05                                     |

| Networking Receptions                                                     | 08                                     |

| Keynotes Presentations                                                    | 09                                     |

| SKYTalk Presentations                                                     | 11                                     |

| TechTalk Presentations                                                    | 13                                     |

| Analyst Presentations                                                     | 14                                     |

| n Memoriam                                                                | 16                                     |

| DAC Awards and Scholarships                                               | 17                                     |

| DAC Pavilion Schedule                                                     | 18                                     |

| Technical Program                                                         |                                        |

| Sunday                                                                    | 19                                     |

|                                                                           |                                        |

| Monday                                                                    |                                        |

| Monday                                                                    | 22                                     |

| Tuesday                                                                   | 22<br>37<br>68                         |

| Tuesday                                                                   | 22<br>37<br>68                         |

| Tuesday                                                                   | 22<br>37<br>68<br>93                   |

| Tuesday .<br>Wednesday .<br>Thursday .                                    | 22<br>37<br>68<br>93<br>98             |

| Tuesday .<br>Wednesday .<br>Thursday .<br>Additional Meetings             | 22<br>37<br>68<br>93<br>98<br>99       |

| Tuesday .<br>Wednesday .<br>Thursday .<br>Additional Meetings<br>LOVE DAC | 22<br>37<br>68<br>93<br>98<br>99<br>00 |

# **CONFERENCE INFORMATION**

# **Exhibit Hours**

# Location: First and Second Floor

**Monday** 10:00 am – 6:00 pm

**Tuesday** 10:00 am – 6:00 pm

**Wednesday** 10:00 am – 4:00 pm

# **Registration Hours**

# Location: Level 1 Lobby

| Saturday  | 12:00 pm – 5:00 pm |

|-----------|--------------------|

| Sunday    | 7:00 am – 7:00 pm  |

| Monday    | 7:00 am – 7:00 pm  |

| Tuesday   | 8:00 am – 6:00 pm  |

| Wednesday | 8:00 am – 6:00 pm  |

|           |                    |

# **Online Proceedings**

To view the proceedings, please visit – www.dac.com/proceedings61

# Stay Connected

Enjoy complimentary WiFi at DAC:

Wifi Network: DAC2024 Wifi Password: 61DAC2024

# First Aid Room

Moscone West First Aid Office is located on the 1st Floor near the Howard Street entrance (behind registration).

Phone: 415.974.4159

REPORT ALL MEDICAL EMERGENCIES IMMEDIATELY

To report a medical emergency, call 511 on a white House Phone, or on a call phone dial 415.974.4021.

# DAC Mobile App

You can download the official conference mobile app in the following ways:

- Search your device's App Store for "DAC Conferences"

- Go to the following link: <u>www.core-apps.com/dl/61dac</u>

Once the DAC Conferences application has downloaded,

- Choose "61st DAC"

- Select to download the event app.

Once you are in the app don't forget to set up your profile by going to the Publish My Profile icon. If you click the box to publish your profile your name (and picture if you upload one) will show in the Attendee icon. From there you can make "Friendships" with other attendees which will allow you to send messages, and set up private appointments.

For technical assistance please contact <a href="mailto:support@core-apps.com">support@core-apps.com</a>

# DAC DIRECTORY MAP: LEVEL 1

SHUTTLE BUS ZONE - HOWARD STREET

# **LEVEL 1 LOBBY**

Registration

# **LEVEL 1 EXHIBIT FLOOR**

Exhibits - Aisles 1300 thru 1500 City Bytes & Beverages Food Court Exhibitor Forum Exhibitor Meeting Rooms 2025 Exhibit Sales Office Community Connection Zone

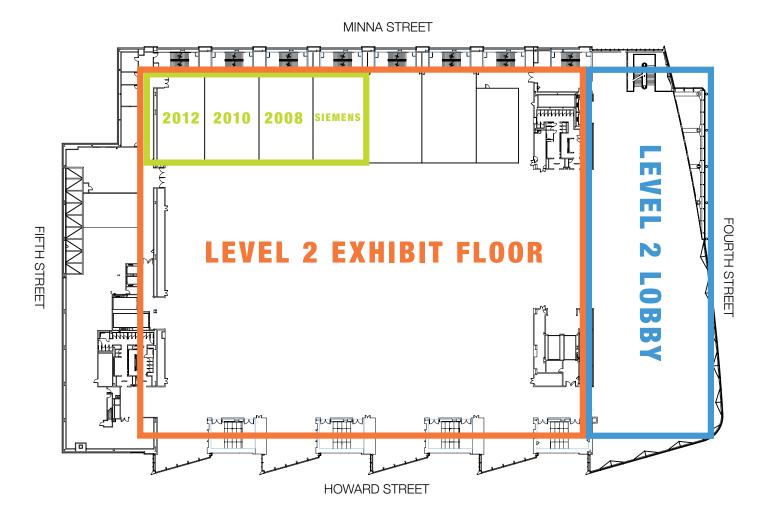

# DAC DIRECTORY MAP: LEVEL 2

# **LEVEL 2 LOBBY**

Networking Receptions

Work-in-Progress & Late Breaking Results Posters

HACK at DAC

Hands-on Training Sessions

PhD Forum/University Demo

# **ROOMS 2008 - 2012**

**Engineering Track Sessions**

# **LEVEL 2 EXHIBIT FLOOR**

Exhibits - Aisles 2300 thru 2500 DAC Pavilion Engineering Track Posters Engineering Track Sessions Press Room

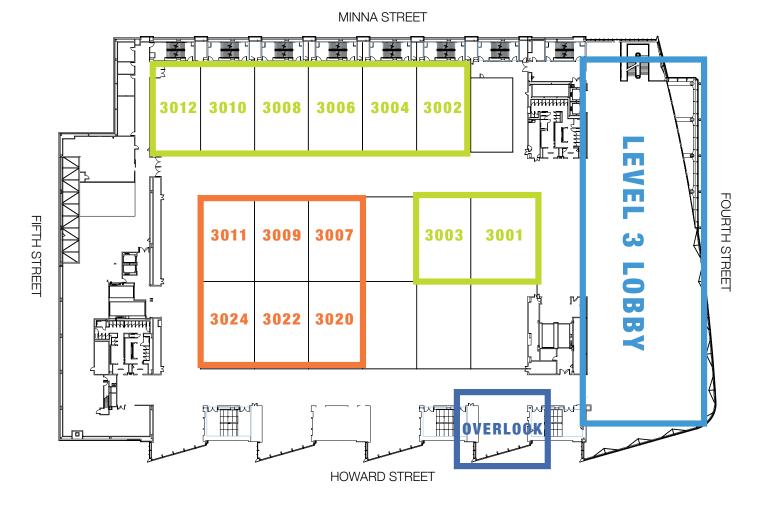

# **DAC DIRECTORY MAP: LEVEL 3**

# **LEVEL 3 LOBBY**

Welcome Reception Speaker Breakfast Career Development Day TPC Reception

# **ROOMS 3001 - 3012**

Research Track Sessions Birds of a Feather Panel Sessions Special Sessions

# ROOM 3007, 3009, 3011, 3020-2024

Keynote (Monday-Wednesday)

# **OVERLOOK**

Speaker Ready Room

# DAC NETWORKING OPPORTUNITIES

# **Networking Receptions**

# Sunday, June 23

Welcome Reception 6:00 pm – 7:00 pm | Level 3 Lobby

# Monday, June 24

Women in Tech Reception 6:00 pm – 7:00 pm | Level 2 Lobby

Engineering Track Poster Session 5:00 pm – 6:00 pm | Level 2 Exhibit Hall

Networking Reception 7:00 pm – 8:00 pm | Level 3 Lobby

# Tuesday, June 25

Engineering Track Poster Session 5:00 pm – 6:00 pm | Level 2 Exhibit Hall

Networking Reception & Work-In-Progress Posters 6:00 pm – 7:00 pm | Level 2 Lobby

# Wednesday, June 26

Networking Reception & Work-in-Progress/Late Breaking Results Poster Session 6:00 pm – 7:00 pm | Level 2 Lobby

# THE CEDA DISTINGUISHED LUNCHEON KEYNOTE

Andrew B. Kahng: AI for EDA and Disruptive Innovation

**Date:** Tuesday, June 25 | **Time:** 12:00 pm – 1:30 pm | **Location:** 3018, 3rd Floor **Speaker:** Andrew Khang, UC San Diego

Recent years have brought a flood of proposed applications for AI and machine learning in EDA. The potential benefits of AI for EDA, including improved design quality with reduced cost and schedule, have attracted significant efforts and focus across both academia and industry. But we have not seen truly disruptive innovation in this space – yet. This talk will examine what disruptive innovations at the AI-EDA nexus might look like. First, what are root causes for the absence of visible disruptions from AI-EDA innovations? These include technical and ecosystem challenges, the time and patience needed to reach tipping points, and the presence of active blockers to innovation. Second, where might advances in AI for EDA bring truly transformative, disruptive innovations to benefit the semiconductor ecosystem? Here, possibilities span analysis and simulation tooling, the nature of design signoff, the EDA-designerfoundry dynamic, and more. There are also basic categories of disruptive innovations: for the EDA business model; for the worldwide ecosystem of academic researchers, EDA vendors, and designers; and for EDA technology itself. Third, and finally, what will accelerate inevitable disruptive innovations, who might deliver them, and how?

Andrew B. Kahng is Distinguished Professor of CSE and ECE and holder of the endowed chair in high-performance computing at UC San Diego. He was visiting scientist at Cadence (1995-97) and founder/CTO at Blaze DFM (2004-06). He is coauthor of 3 books and over 500 journal and conference papers, holds 35 issued U.S. patents, and is a fellow of ACM and IEEE. He was the 2019 Ho-Am Prize laureate in Engineering. He has served as general chair of IEEE CEDA-sponsored conferences such as DAC, ISPD, SLIP and MLCAD, and from 2000-2016 served as international chair/co-chair of the International Technology Roadmap for Semiconductors (ITRS) Design and System Drivers working groups. He was the principal investigator of the U.S. DARPA "OpenROAD" project (https://theopenroadproject.org/) from June 2018 to December 2023, and until August 2023 served as principal investigator and director of "TILOS" (https://tilos.ai/), a U.S. NSF AI Research Institute.

# **KEYNOTE PRESENTATIONS**

JIM KELLER

CEO, TENSTORRENT

# **Building AI with RISC-V**

Monday, June 24 | 8:45 am - 9:45 am

How Tenstorrent built our first two generations of AI products. We'll tell you what went well, what went wrong and what we're doing next.

**ABOUT:** Jim Keller is CEO of Tenstorrent and a veteran hardware engineer. Prior to joining Tenstorrent, he served two years as Senior Vice President of Intel's Silicon Engineering Group. He has held roles as Tesla's Vice President of Autopilot and Low Voltage Hardware, Corporate Vice President and Chief Cores Architect at AMD, and Vice President of Engineering and Chief Architect at P.A. Semi, which was acquired by Apple Inc. Jim has led multiple successful silicon designs over the decades, from the DEC Alpha processors, to AMD K7/K8/K12, HyperTransport and the AMD Zen family, the Apple A4/A5 processors, and Tesla's self-driving car chip.

# **DR. GARY PATTON**

CORPORATE VICE PRESIDENT AND GENERAL MANAGER OF THE DESIGN ENABLEMENT GROUP IN TECHNOLOGY DEVELOPMENT, INTEL CORPORATION

# Systems Foundry - A Journey from 'System on a Chip' to 'System of Chips'

# Tuesday, June 25 | 8:45 am - 9:45 am

In this keynote, Dr. Gary Patton will introduce the fundamental concepts driving the vision of a 'Systems Foundry', including a standardsbased approach to assemble heterogenous dies. Dr. Patton will also cover the factors driving the inevitable need for disaggregation; factors like reticle limit, thermal constraints, cost, yield, etc., among others that are especially exacerbated in the need to satisfy the demands of HPC designs in the AI era. In addition, Dr. Patton will go over the transformative journey at Intel over the last 4-5 years that has helped orient the execution towards enabling the vision of a Systems Foundry. A journey that encompasses delivering to a full breadth of EDA offerings and development of advanced packaging capabilities, to name a few. The work is not done, however; the EDA & IP ecosystem has a vital role to play in this vision - to enable a seamless 3DIC design platform for advanced packaging implementation & modeling, AI-driven 3D exploration and System-Technology Co-Optimization while tackling challenges in the multi-physics domain. Intel has several collaborative projects with EDA to address these challenges, and Dr. Patton will end with a call to action to the ecosystem partners on continued partnership to realize this vision

**ABOUT:** Dr. Gary L. Patton is corporate vice president and general manager of the Design Enablement group in Technology Development at Intel Corporation. Design Enablement is charged with delivering the Process Design Kits (PDKs), Test-Chips, Design-Technology Co-Optimization (DTCO), and Foundational IP (FIP) & Embedded Memory Solutions to maximize technology value and meet customer needs and schedules. Prior to joining Intel, Dr. Patton served as is the Chief Technology Officer and Senior Vice President of Worldwide Research and Development and Design Enablement at GlobalFoundries where he was responsible for the semiconductor technology R&D roadmap, operations, and execution. Prior to that, Dr. Patton was vice president of IBM's Semiconductor Research and Development Center — a position that he held for eight years where he was responsible for IBM's Semiconductor technology R&D with over 30 years of semiconductor experience. He is a Fellow of the IEEE and recipient of the 2017 IEEE Frederik Philips Award for industry influence and leadership in the development of leading-edge microelectronics technology and collaborative research. In 2016, Dr. Patton was inducted into the VLSI Research Hall of Fame for his contributions to the advancement of the semiconductor industry over several decades. Dr. Patton received his bachelor's degree in electrical engineering from UCLA and his master's and Ph.D. degrees in electrical engineering from Stanford University

# **KEYNOTE PRESENTATIONS** continued

# ALAN LEE

CHIEF TECHNOLOGY OFFICER, ANALOG DEVICES, INC. (ADI).

# Al and the Intelligent Edge

Wednesday, June 26 | 8:45 am - 9:45 am

Artificial intelligence is changing the world around us, but most of the focus has been on large models running on immense compute servers. There is a critical need for AI in edge applications to decrease latency and power consumption. Fulfilling this need requires new approaches to meet the constraints of future industrial, automotive, and consumer platforms at the intelligent edge.

**ABOUT:** As Chief Technology Officer, Alan Lee develops and leads ADI's long-term technology strategy for applications across the company's end markets, working closely with ADI's global business units and manufacturing operations to drive ADI's competitive advantage. Alan is responsible for identifying, sourcing, and cultivating new business, technology, and research opportunities, as well as developing foundational technology capabilities in support of the current and future needs of our markets and customers. Alan is a highly accomplished executive with over 20 years of experience in the technology industry. Most recently he served as the Corporate Vice President of Research and Advanced Development at AMD. During his tenure at the company, he founded AMD Research where he oversaw the company's worldwide research and advanced technology labs, university engagements, and external research contracting. Alan also led extreme-scale computing technology at AMD, where he drove the software and hardware engineering efforts to build the world's fastest platforms for machine learning, industrial, and scientific applications.

# SARITA V. ADVE

RICHARD T. CHENG PROFESSOR, UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN

# **Enabling the Era of Immersive Computing**

# Thursday, June 27 | 8:45 am - 9:45 am

Immersive computing (including virtual, augmented, mixed, and extended reality, metaverse, digital twins, and spatial computing) has the potential to transform most industries and human activities to create a better world for all. Delivering on this potential, however, requires bridging an orders of magnitude gap between the power, performance, and quality-of-experience attributes of current and desirable immersive systems. With a number of conflicting requirements - 100s of milliwatts of power, milliseconds of latency, unbounded compute to realize realistic sensory experiences – no silver bullet is available. Further, the true goodness metric of such systems must measure the subjective human experience within the immersive application. This talk calls for an integrative research agenda that drives codesigned end-to-end systems from hardware to system software stacks to foundation models spanning the end-user device/edge/cloud, with metrics that reflect the immersive human experience, in the context of real immersive applications. I will discuss work pursuing such an approach as part of the IMMERSE Center for Immersive Computing which brings together immersive technologies, applications, and human experience, and in the ILLIXR project based on an open-source end-to-end system to democratize immersive systems research.

**ABOUT:** Sarita Adve is the Richard T. Cheng Professor of Computer Science at the University of Illinois Urbana-Champaign where she directs IMMERSE, the Center for Immersive Computing. Her research interests span the system stack, ranging from hardware to applications. Her work on the data-race-free, Java, and C++ memory models forms the foundation for memory models used in most hardware and software systems today. Her group released the ILLIXR (Illinois Extended Reality) testbed, an open-source extended reality system and research testbed, and launched the ILLIXR consortium to democratize XR research, development, and benchmarking. She is also known for her work on heterogeneous systems and software-driven approaches for hardware resiliency. She is a member of the American Academy of Arts and Sciences, a fellow of the ACM and IEEE, and a recipient of the ACM/IEEE-CS Ken Kennedy award. As ACM SIGARCH chair, she co-founded the CARES movement, winner of the CRA distinguished service award, to address discrimination and harassment in Computer Science research events. She received her PhD from the University of Wisconsin-Madison and her B.Tech. from the Indian Institute of Technology, Bombay.

# **SKYTALK PRESENTATIONS**

# **DR. JAY LEWIS**

DIRECTOR OF THE NATIONAL SEMICONDUCTOR TECHNOLOGY CENTER (NSTC) PROGRAM, CHIPS R&D OFFICE AT THE DEPARTMENT OF COMMERCE

# CHIPS for America and Sustained U.S. Leadership: A Vision for Innovation Through the National Semiconductor Technology Center (NSTC)

Monday, June 24 | 1:00 pm - 1:45 pm | DAC Pavilion, Level 2 Exhibit Hall

The semiconductor industry has always moved fast, but changes in the industry over recent years have been historic. We will discuss a variety of challenges in the ecosystem, and how the NSTC can unite the community to address those challenges. Some of these are technical – logic, mixed signal, memory, photonics, design / co-design, and architecture all need new breakthroughs to continue to advance the state of technology. Others are ecosystem challenges. Access to design tools, IP, and collaboration environments, as well as increasing use of AI in the design and verification flow will all transform the way that the industry does its work. Access to advanced R&D facilities and leading-edge shuttles can accelerate the pace of research. The traditional venture model has been mismatched with hardware investments for decades, and this has been a drag on innovation, but there are new ideas for how this can work better. In closing, we will provide updates on the priorities for this year and show how the NSTC can change the long-term trajectory for innovation.

**ABOUT:** Dr. Jay Lewis is the Director of the National Semiconductor Technology Center, or NSTC, Program, for the CHIPS R&D Office at the Department of Commerce. In this role he is working to establish the NSTC program, a public-private consortium that will serve as a cornerstone of semiconductor research for the country. He previously worked at Microsoft, at DARPA, and had an early career in semiconductor research.

Dr. Lewis is a Fellow of the American Vacuum Society and is an IEEE and SPIE Senior Member. He has published over 50 articles in technical journals and conference proceedings and holds eleven U.S. patents. He received a Bachelor's degree in Materials Science from the Georgia Institute of Technology, and a Ph.D. in Materials Science and Engineering from the University of Florida.

# NIELS FACHÉ

VP & GM, KEYSIGHT EDA

# New EDA Methodologies are Transforming Engineering Lifecycle Management

# Tuesday, June 25 | 1:00 pm - 1:45 pm | DAC Pavilion, Level 2 Exhibit Hall

This talk provides a broad, visionary perspective about the dynamic changes impacting electronic design automation tools and methodologies and their pivotal role in re-shaping engineering lifecycle management. It explains the trend toward convergence of EDA and CAE domains to address exploding system complexity and deliver multi-disciplinary solutions. Future workflows must incorporate digital threads that connect virtual prototypes and digital twins with physical systems. Predictive simulation and analysis across domains is key to accelerating engineering lifecycles.

Rapid industry adoption of AI, heterogeneous integrated circuits and chiplet technologies, software automation using scripting languages, and comprehensive data and intellectual property management tools is driving a seismic shift in design and verification methodologies. This talk covers how these EDA technologies contribute to more efficient and effective enterprise lifecycles. Application of these technologies must elevate RF, microwave, and mixed-signal design to an equal footing with digital design to achieve modernization of engineering workflows.

**ABOUT:** Niels Faché is responsible for Keysight's design and simulation portfolio. In his most recent positions, he was Vice President and General Manager of the Remarketing Solutions Division and then the Keysight Services Portfolio Organization, both part of Keysight's Global Services Organization (KGSO). Niels joined Hewlett Packard in 1994, when HP acquired Alphabit, a start-up software company in Belgium. He was co-founder and CEO of Alphabit, which developed the electromagnetic simulator Momentum - now part of the PathWave Advanced Design System (ADS). During his career, Niels has since held a variety of R&D, marketing, product planning and general management positions at HP, Agilent and Keysight in Electronic Design Automation, Test and Measurement Product Lines and Services. His roles have often involved leveraging technology and talented teams to transform and grow organizations into front-runners. He is based in Santa Clara, California. Niels holds a master's degree and Ph.D. in electrical engineering, both from the University of Ghent, Belgium, where he also served as a part-time professor from 1995 to 1997. He has a business degree from the Université Libre de Bruxelles, Belgium, and has completed coursework at the Stanford Center for Professional Development.

# SKYTALK PRESENTATIONS CONTINUED

# **VIJI SRINIVASAN**

DISTINGUISHED RESEARCH STAFF MEMBER, IBM

# Al Acceleration Roadmap: Co-Designing Algorithms, Hardware, and Software

Wednesday, June 26 | 1:00 pm - 1:45 pm | DAC Pavilion, Level 2 Exhibit Hall

Deep Neural Networks (DNNs) have become state-of-the-art in a variety of machine learning tasks spanning domains across vision, speech, and machine translation. Deep Learning (DL) achieves high accuracy in these tasks at the expense of 100s of ExaOps of computation. Hardware specialization and acceleration is a key enabler to improve operational efficiency of DNNs, in turn requiring synergistic cross-layer design across algorithms, hardware, and software.

In this talk I will present this holistic approach adopted in the design of a multi-TOPs AI hardware accelerator. Key advances in the AI algorithm/application-level exploiting approximate computing techniques enable deriving low-precision DNNs models that maintain the same level of accuracy. Hardware performance-aware design space exploration is critical during compilation to map DNNs with diverse computational characteristics systematically and optimally while preserving familiar programming and user interfaces. The opportunities to co-optimize the algorithms, hardware, and the software provides the roadmap to continue to deliver superior performance over the next decade.

**ABOUT:** Viji Srinivasan is a Distinguished Research Staff Member and a manager of the accelerator architectures and compilers group at the IBM T.J. Watson Research Center in Yorktown Heights. At IBM, she has worked on various aspects of data management including energy-efficient processor designs, microarchitecture of the memory hierarchies of large-scale servers, cache coherence management of symmetric multiprocessors, accelerators for data analytics applications and more recently end-to-end accelerator solutions for Al. Many of her research contributions have been incorporated into IBM's Power & System-z Enterprise-class servers.

# **TECHTALK PRESENTATIONS**

# **JUAN REY**

VICE PRESIDENT OF GOVERNMENT PROGRAMS, SIEMENS

# The Evolution of the Digital Twin in Semiconductor Design and the Central Role AI Plays

Tuesday, June 25 | 11:15 am - 12:00 pm | DAC Pavilion, Level 2 Exhibit Hall

Depending on who you talk with the Digital Twin is either the newest thing in semiconductor, or something that semiconductor has always had. The truth is that both are true. Semiconductor has long relied on domain specific Digital Twins of different aspects of the design in order to design, test, and integrate in the virtual world before committing to manufacture. Starting with the Siemens acquisition of EDA, but now being talked about more widely, we now talk about the Comprehensive Digital Twin of the design, which attempts to more completely capture the design and allow analysis using not only traditional EDA but also Multiphysics. This is just the beginning however, as we are already moving towards the merging of the Design Digital Twin, with the Manufacturing Digital Twin to enable closed loop manufacturing aware design.

This evolution brings with it new challenges of exponentially increasing complexity, and multiple disparate engineering domains that need to work together. It is here where AI is coming to the rescue to help guide where engineers need to focus their effort, encapsulate domain knowledge that they need to perform a task, and transform data between different domains either directly or via surrogate models.

In this presentation we will explore the way this evolution has affected IC and product design tools, the benefits it has brough to design teams, what the future holds, and how closed-loop manufacturing aware design will bring in a new era of design.

**ABOUT:** Juan C. Rey, vice-president of government programs, previous vice president of Engineering, Calibre, joined Mentor in 2001 as senior engineering director for Mentor's industry-leading Calibre product line, directing all development activities for Calibre products.

Previously he was vice-president of Engineering at Exend Corporation, managing all software development and quality activities. Prior to that he was engineering director for Physical Verification at Cadence Design Systems.

Earlier positions include: manager/developer for Process Modeling and Parasitic Extraction at Technology Modeling Associates; visiting scholar/science and engineering associate at Stanford University; senior research engineer at INVAP, Argentina; and associate professor at Universidad Nacional del Comahue, Argentina.

Juan holds a degree in Nuclear Engineering from Instituto Balseiro, Universidad Nacional de Cuyo, Argentina. The author or co-author of numerous papers and conference presentations, he serves on the Executive Technology Advisory Board of Semiconductor Research Corporation (SRC) and previously at the SI2 Board of Directors and the Industry Advisory Board of the UCLA Center for Domain-Specific Computing.

# ANALYST PRESENTATIONS

# **JAY VLEESCHHOUWER**

SENIOR INDUSTRY ANALYST COVERING ENGINEERING AND ENTERPRISE SOFTWARE, GRIFFIN SECURITIES

# **A View from Wall Street**

Monday, June 24 | 10:15 am - 11:00 am | DAC Pavilion, Level 2 Exhibit Hall

We will examine the financial performance and key business metrics of the EDA industry through 2023, as well as the material technical and market trends and requirements that have influenced EDA business performance and strategies. Among the trends, we will again examine the progression of semiconductor R&D spending and how the market value of the publicly held EDA companies has evolved. Lastly, we will provide our updated financial projections for the EDA industry for 2024 through 2026.

**ABOUT:** Mr. Vleeschhouwer has over four decades of research experience. He is a senior industry analyst covering Engineering and Enterprise Software, responsible for fundamental research of companies under coverage, including the regular publication of proprietary company and industry reports and detailed company and industry financial modeling. Principal industry reports include The Software Standard (software industry commentary, news, data, and analysis) and The State of EDA (quarterly in-depth review of electronic design automation). Ranked by Refinitiv Starmine Analyst Awards (U.S.) #1 in "top stock pickers" for software (2020). He has been regularly invited to present at software and other industry conferences, in addition to broadcast media appearances and other print and online media

# **DYLAN PATEL**

CHIEF ANALYST, SEMIANALYSIS

# **Designing an ASIC for the Generative AI Era**

Tuesday, June 25 | 10:15 am - 11:00 am | DAC Pavilion, Level 2 Exhibit Hall

The presentation will cover what is required to design an ASIC for the Generative AI Era. It will cover the compute, networking, and memory constraints of generative AI as well as what companies are doing to push beyond it with optics, packaging, and system level design.

**ABOUT:** Dylan Patel is the founder and Chief Analyst of SemiAnalysis, a semiconductor and AI research company. SemiAnalysis has analysts across the US, Japan, Taiwan, Singapore, and France covering the industry from production of materials, equipment, process technology, fabs to design IP and fabless to physical infrastructe of datacenters, networking, and AI models.

# ANALYST PRESENTATIONS CONTINUED

# **TOM HACKENBERG**

PRINCIPAL ANALYST FOR COMPUTING AND SOFTWARE IN THE SEMICONDUCTOR, MEMORY AND COMPUTING DIVISION, YOLE INTELLIGENCE

# Chiplets – The Next Generation Chip Design Trend Beyond Moore's Law

# Wendesday, June 26 | 10:15 am - 11:00 am | DAC Pavilion, Level 2 Exhibit Hall

The next stage of integrated circuit manufacturing is disaggregation or breaking up the design of large chips into smaller units. These smaller units typically represent a unique function. The advantages are shorter design time, lower cost, easier drop-in inclusion of already available designs, increased modularity and scalability, and fewer manufacturing defects. This technique is especially well suited for leveraging the heterogeneous nature of large processors, coprocessors, system on chip (SoC) and integrated memory solutions, but the evolution of this trend is likely to spread throughout IC design.

This presentation is designed to provide a brief introduction to the nature of chiplet design and why it is so important at this time. The technical details will be presented in moderation including teardown examples of current chiplet solutions and which end-systems include them. The presentation will touch on technology advances that need to evolve to facilitate this approach. We will provide a market penetration and a five-year forecast for chiplet-based design strategies. We will provide longer views of the evolution to include such ICs as graphics, AI, and other accelerators, FGPAs, microcontrollers and other processors. We will conclude with why we think this trend is essential to the future of the semiconductor industry and design automation.

**ABOUT:** Tom Hackenberg is a Principal Analyst for Computing and Software in the Semiconductor, Memory and Computing Division at Yole Intelligence, part of Yole Group. Tom is an industry leading expert reporting on markets for semiconductor processors including CPUs, MPUs, MCUs and DSPs, SoCs, GPUs and discrete accelerators, FPGAs, and configurable processors since 2006. Tom is also well-versed in related technology trends including AI and edge computing, IoT, heterogeneous processing, chiplets, as well as vertical markets like Automotive, Computing and Telecommunications where processor trends play a significant role.

Tom has appeared as a presenter on these topics at associated events as the Chiplet Summit, OCP ODAS Workshop on Chiplets, Rosenblatt's Age of Al Scaling, System-on-Chip Conference, Vision and Al Summit, Xilinx Adapt: Automotive: Anywhere, Yole's Live Market Briefings and as well as custom proprietary presentations. He can also be found quoted or bylined in news and trade publications such as Cision, Computerworld, Design and Reuse, EE|Times & EE|Times Asia, Fierce Electronics, Insider, Semi Engineering, VentureBeat, and more for expertise on the processor market.

Tom worked with market-leading processor suppliers developing both syndicated and custom research. He holds a BSEE/BSECE from the University of Texas at Austin specializing in Processors and FPGAs.

# **IN MEMORIAM**

# Chris Spear 1960 - 2024

Chris Spear, a long-time veteran of our industry, passed away suddenly last February. Chris joined Mentor/ Siemens EDA as a principal customer training engineer in 2016 drawing on his extensive background as an applications engineer working closely with verification engineers in his previous roles. He literally wrote the book on "SystemVerilog for Verification" and his dedication and passion for sharing his knowledge led

to his pivotal role in shaping Siemens EDA's training strategies in the design verification domain. During his tenure, Chris's live training classes on SystemVerilog and UVM proved invaluable to hundreds of engineers, offering an unmatched educational experience to both new and seasoned engineering professionals. This is a quote from a verification engineer who attended Chris's advanced UVM class shortly before his passing: "I really enjoyed the in-class instruction of Chris Spear; his willingness to impart, engage and understand makes him an invaluable resource and highly effective instructor."

Chris's love for his family knew no bounds. He was an avid cyclist and enjoyed spending time in nature during his cycling expeditions and explorations at home and in various countries around the globe. Many of you may be familiar with and have supported Chris's decades-long participation in the Pan-Mass Challenge, an annual bike-a-thon for life-saving cancer research and treatment at Dana Farber Cancer Institute, for which Chris fundraised and rode every summer.

In Siemens EDA and the design verification communities, we mourn the loss of a dear friend and colleague, and the world has lost an exceptional individual. Our deepest condolences go to his family, friends, and colleagues.

# Lynn Ann Conway (1938 - 2024)

Lynn Ann Conway was an American computer scientist, electrical engineer and transgender activist. She worked at IBM in the 1960s and invented generalized dynamic instruction handling, a key advance used in out-of-order execution, used by most modern computer processors to improve performance.

Lynn initiated the Mead–Conway VLSI chip design revolution in very large scale integrated (VLSI) microchip design. That revolution spread rapidly through the research universities and computing industries during the 1980s, incubating an emerging electronic design automation industry, spawning the modern 'foundry' infrastructure for chip design and production, and triggering a rush of impactful high-tech startups in the 1980s and 1990s

# DAC AWARDS AND SCHOLARSHIPS

# 2024 DAC UNDER-40 INNOVATORS AWARD

In recognition for technical contributions of notable impact in the field of design and automation of electronic circuits and systems

### Nishant Patil, Apple

Bei Yu, Chinese University of Hong Kong

Bita Darvish Rouhami, Nvidia

Jingtong Hu, University of Pittsburgh

Farimah Farahmandi, University of Florida

# 2024 MARIE R. PISTILLI WOMEN IN ENGINEERING ACHIEVEMENT AWARD

For displaying equality, diversity, and acceptance while visibly helping to advance women in electronic design

Sashi Obilisetty, Synopsys

# ACM/SIGDA

# ACM TODAES ROOKIE AUTHOR OF THE YEAR (RAY) AWARD

Wenjing Jiang, University of Minnesota

### **2024 ACM TODAES BEST PAPER AWARD**

Shanshi Huang, Hongwu Jiang, Shimeng Yu, Georgia Tech

### ACM SIGDA DISTNGUISHED SERVICE AWARD

Marilyn Wolf, University of Nebraska-Lincoln Patrick Haspel, Synopsys, Inc.

ACM SIGDA OUTSTANDING NEW FACULTY AWARD

Bonan Yan, Peking University

### **ACM FELLOWS**

Anand Raghunathan, Purdue UniversityRolf Drechsler, University of BremenMassoud Pedram, University of Southern California

ACM SIGDA OUTSTANDING PH.D. DISSERTATION AWARD

# Lukas Burgholzer, Johannes Kepler University SIGDA PIONEERING ACHIEVEMENT AWARD

John Darringer, IBM Research

### **SIGDA SERVICE AWARD**

Weiwen Jiang, George Mason UniversityYu-Guang (Andy) Chen, National Central University, TaiwanFan Chen, Indiana UniversityAhmad Sadeghi, TU Darmstady

# IEEE/CEDA

# **IEEE CEDA OUTSTANDING SERVICE AWARD**

For outstanding service to the EDA community as DAC General Chair in 2022

Jorg Henekl, Karlsruhe Institute of Technology

### **IEEE FELLOWS**

Jinjun Xiong, University of Buffalo

Qinru Qiu, Syracuse University

Haoxing Ren, NVIDIA

Sudeep Pasricha, Colorado State University

Sri Parameswaran, The University of New South Wales

Lei He, UCLA

Tsung-Yi Ho, The Chinese University of Hong Kong

# IEEE/ACM A RICHARD NEWTON TECHNICAL IMPACT AWARD IN ELECTRONIC DESIGN AUTOMATION

Mircea Stan, University of Virginia

Wayne Burleson, University of Massachusetts Amherst

# IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS DONALD 0. PEDERSON BEST PAPER AWARD

PACT: An Extensible Parallel Thermal Simulator for Emerging Integration and Cooling Technologies

Zihao Yuan, Boston University

Prachi Shukla, Boston University

Sofiane Chetoui, Boston University

Sean Nemtzow, Boston University

Sherief Reda, Boston University

Ayse K Coskun, Boston University

An Open-Source Framework for FPGA Emulation of Analog/Mixed-Signal Integrated Circuit Designs

Steven Herbst, Stanford University

Gabriel Rutsch, Infineon Technologies AG, Germany

Wolfgang Ecker, Infineon Technologies AG, Germany

Mark Horowitz, Stanford University

### IEEE GUSTAV ROBERT KIRCHOFF AWARD

Mary Jane Irwin, Pennsylvania State University

# 2024 PHIL KAUFMAN AWARD FOR DISTINGUISHED CONTRIBUTIONS TO ESD

For overall impact on Electronics industry through contributions to scan design for testability, related test automation.

Lawrence Pileggi, Carnegie-Mellon University

# **DAC PAVILION SCHEDULE**

The location for all events is: DAC Pavilion | Level 2 Exhibit Hall

# Monday, June 24

# 10:15 am – 11:00 am

ANALYST REVIEW: A VIEW FROM WALL STREET

Speaker: Jay Vleeschhouwer, Griffin Securities

### 11:15 am - 12:00 pm

#### PANEL: BEST OF BOTH WORLDS: BRIDGING THE GAPS IN ENGINEERING SOFTWARE FOR SEMICONDUCTORS AND SYSTEMS

Moderator: Jay Vleeschhouwer, Griffin Securities

Panelists: Tom Beckley, Cadence Design Systems, Inc.; Philippe Laufer, Dassault Systemes; Niels Fache, Keysight; Paul Sagar, PTC; Tony Hemmelgarn, Siemens; Shankar Krishnamoorthy, Synopsys

#### 1:00 pm – 1:45 pm

### SKYTALK: CHIPS FOR AMERICA AND SUSTAINED U.S. LEADERSHIP: A VISION FOR INNOVATION THROUGH THE NATIONAL SEMICONDUCTOR TECHNOLOGY CENTER (NSTC)

Speaker: Dr. Jay Lewis, Director of the National Semiconductor Technology Center (NSTC) Program CHIPS R&D Office at the Department of Commerce

#### 2:00 pm – 2:45 pm

#### PANEL: A NEW DESIGN VERIFICATION ERA AS OPEN-SOURCE UPENDS THE STATUS QUO

Moderator: Ron Wilson, Ojo-Yoshida Report

Panelists: Jean-Marie Brunet, Siemens; Darren Jones, Andes; Josh Scheid, Ventana Microsystems; Ty Garibay, Condor Computing

### 3:00 pm – 3:45 pm

#### **COOLEY'S DAC TROUBLEMAKER PANEL**

- Moderator: John Cooley, Deepchip

- Panelists: Tony Hemmelgarn, Siemens; Shankar Krishnamoorthy, Synopsys; Paul Cunningham, Cadence Design Systems, Inc.; Dean Drako, IC Manage; Prakash Narain, Real Intent; Joe Costello, Metrics

4:30 pm - 5:30 pm GLADIATOR ARENA POSTER BATTLE

# Tuesday, June 25

#### 10:15 am - 11:00 am

ANALYST REVIEW: DESIGNING AN ASIC FOR THE GENERATIVE AI ERA

Speaker: Dylan Patel, SemiAnalysis

#### 11:15 am - 12:00 pm

TECHTALK: THE EVOLUTION OF THE DIGITAL TWIN IN SEMICONDUCTOR DESIGN, AND THE CENTRAL ROLE AI PLAYS

Speaker: Juan Rey, Siemens

#### 1:00 pm – 1:45 pm

SKYTALK: NEW EDA METHODOLOGIES ARE TRANS-FORMING ENGINEERING LIFECYCLE MANAGEMENT Speaker: Niels Fache, Keysight

2:00 pm – 2:45 pm

#### PANEL: BLACKOUT - MANAGING KW POWER BUDGETS

Moderator: Ed Sperling, Semiconductor Engineering

Panelists: Joe Davis, Siemens; Mo Faisal, Movellus; Trey Roessig, Empower; Dean Wallace, Marvell; Hans Yeager, Tenstorrent

### 3:00 pm – 3:45 pm

#### PANEL: ADVANCING CHIP SECURITY TO MEET HEIGHTENED REQUIREMENTS

Moderator: Ann Mutscher, Semiconductor Engineering

Panelists: Andreas Kuehlmann, Cycuity; Neeraj Paliwal, Rambus; Victoria Coleman, US Air Force; Vivek Tiwari, Intel

### 4:30 pm - 5:30 pm

**GLADIATOR ARENA POSTER BATTLE**

# Wednesday, June 26

### 10:15 am - 11:00 am

ANALYST REVIEW: CHIPLETS – THE NEXT GENERATION CHIP DESIGN TREND BEYOND MOORE'S LAW Speaker: Tom Hackenberg, Yole Group

#### 11:15 am - 12:00 pm

# PANEL: FROM DESIGN TO DEFENSE: SHAPING THE FUTURE OF MICROELECTRONICS SECURITY

Moderator: Nitin Dahadembedded.com

Panelists: Cayley Rice, Leidos; Margaret Schmitt, Amida Technology Solutions; Mark Tehranipoor, University of Florida; Simha Sethumadhavan, Columbia University/Chip Scan Inc.

#### 1:00 pm – 1:45 pm

# SKYTALK: AI ACCELERATION ROADMAP: CO-DESIGNING ALGORITHMS, HARDWARE, AND SOFTWARE

Speaker: Viji Srinivasan, IBM Thomas J. Watson Research Center

2:00 pm – 2:45 pm GLADIATOR ARENA POSTER BATTLE

### 3:00 pm – 3:45 pm

ENGINEER TRACK BEST PAPER AWARD & GLADIATOR AWARDS ANNOUNCEMENT

### Program accurate as of June 17, 2024.

Locations listed for each speaker are representative of where they live, not where their corporate office is located.

# FULL PROGRAM

### DCGAA 2024: INTERNATIONAL WORKSHOP ON DL-HARDWARE CO-DESIGN FOR GENERATIVE AI ACCELERATION)

Time: 8:00 AM – 12:00 PM Session Type: Workshop Topic Area(s): Al Room: 3004, 3rd Floor

**Organizer(s):** Dongkuan Xu, North Carolina State University, Raleigh, NC; Hua Wei, Arizona State University, Tempe, AZ; Ang Li, University of Maryland, College Park, MD; Tinoosh Mohsenin, Johns Hopkins University, Baltimore, MD; Peipei Zhou, University of Pittsburgh, Pittsburgh, PA; Caiwen Ding, University of Connecticut, Storrs, CT; Yingyan (Celine) Lin, Georgia Institute of Technology, Atlanta, GA; Yanzhi Wang, Northeastern University, Boston, MA

Description: In the ever-evolving domain of computational technologies, the profound impact of artificial intelligence (AI) is indisputable. The DCgAA 2024 Workshop stands at the forefront of this revolution, offering an essential platform for synergizing deep learning (DL) models with advanced hardware system designs. This second iteration of our workshop is dedicated to exploring and fortifying the symbiotic relationship between DL and hardware innovation, especially in the context of generative AI applications. Deep learning's integration across various computing sectors necessitates robust hardware solutions to amplify model performance and efficiency. However, current DL research often overlooks critical real-world computational constraints such as power efficiency, memory usage, and scalability of model sizes. This oversight limits the practical deployment of Al innovations, particularly in scenarios requiring high computational efficiency like mobile devices, AR/VR technologies, and other edge computing environments. Our workshop aims to bridge this gap by fostering discussions and research on optimizing hardware designs specifically tailored for generative AI applications. We will delve into the unique computational demands of these models and the necessity of hardware systems that can adapt to their complex requirements. This approach is pivotal for realizing the full potential of DL innovations and ensuring their effective application in real-world scenarios.

Sunday, June 23, 2024

### IN-MEMORY ARCHITECTURES AND COMPUTING APPLICATIONS WORKSHOP (IMACAW) -3RD EDITION

Time: 8:00 AM – 5:00 PM Session Type: Workshop Topic Area(s): Design Room: 3001, 3rd Floor

**Organizers:** Albert Bosio, Lyon Institute of Nanotechnology, Lyon, France; Nima TaheriNejad, Heidelberg University, Heidelberg, Germany; Deliang Fan, Johns Hopkins University, Baltimore, MD

**Description:** Today's computer architectures and device technologies used to manufacture them are facing major challenges, rendering them incapable of delivering the performances required by complex applications such as Big-Data processing and Artificial Intelligence (AI). The iMACAW workshop aims at providing a forum to discuss In-Memory-Computing (as an alternative architecture) and its potential applications. To this end, we take a cross-layer and cross-technology approach covering State-of-the-Art (SoA) works that use SRAM, DRAM, FLASH, RRAM, PCM, MRAM, or FeFET as their memory technology. The workshop also aims at reinforcing the In-Memory-Computing (IMC) community and at offering a holistic vision of this emerging computing paradigm to the design automation communities. This workshop proposal follows the two previous editions hosted in DAC1, it will provide an opportunity for the audience to listen to invited speakers who are pioneers of the field, learn from them, ask questions, and interact with them. Open submission contributors also get the opportunity to share their knowledge, present their most-recent work, and their work in progress with the community, interact with other experts in the field, and receive feedback.

Research Sessions Special Panel Session Workshop; Hands-on Labs

Tutorial

Exhibitor DAC Pav Forum Analy

DAC Pavilion Panel; Te Analyst Review S

TechTalk Keynotes and SKYTalk Visionary Talks

### Sunday, June 23, 2024

# SSH-SOC: SAFETY AND SECURITY IN HETEROGENEOUS OPEN SYSTEM-ON-CHIP PLATFORMS

Time: 8:00 AM – 5:00 PM Session Type: Workshop Topic Area(s): Security Room: 3002, 3rd Floor

**Organizer(s):** Francesco Restuccia, University of California, San Diego, CA; Angelo Garofalo, University of Bologna, Bologna, Italy; Biruk Seyoum, Columbia University, New York City, NY; Luca Benini, ETH Zurich, Zurich, Switzerland

**Description:** The diminishing returns of technology scaling on performance have paved the way for innovation in computer architecture, shifting towards heterogeneous, domain-specific architectures. Modern systems incorporate domain-specific accelerators and specialized system components (buses, network-on-chip, peripherals, sensors, etc..) to efficiently manage complex and computationally demanding workloads.

A widely adopted approach to reduce the System-on-Chip (SoC) design complexity involves a hierarchical strategy that differentiates the system design efforts for the components of the heterogeneous architecture. This encompasses: (i) expensive in-house RTL development for critical modules, (ii) leveraging the most recent high-level synthesis (HLS) tools, and/or (iii) outsourcing highly specialized third-party intellectual property (IP) modules to reduce costs and development time.

Despite its advantages, such diversified design methodology exacerbates the challenge of system integration. Moreover, recent studies have demonstrated how careless system integration can lead to dangerous conditions, impacting the security, safety, and performance of the system. This can result from a combination of factors, including development bugs, lack of specifications, superficial verifications of IP components' behavior at the system level, and a scarcity of mechanisms supporting safe and secure system execution.

Addressing these challenges requires innovative approaches in the design and verification process, especially when dealing with the stringent safety and security requirements of mission-critical systems. The research community can play a disruptive role in overcoming these challenges. The availability of the complete codebase of multiple mature open hardware architectures and reconfigurable platforms represents an unprecedented opportunity for the development, testing, and native integration of novel mechanisms, tools, and analysis supporting security, safety, and performance efficiency for the development of the next-generation of systems.

This workshop welcomes work-in-progress contributions and innovative directions aimed at addressing challenges and profit from the opportunities provided by open hardware designs and architectures for the development of next-generation heterogeneous SoCs. The topics for the workshop include, but are not restricted to:

- · Security verification for hardware designs and system architectures

- Architectural aspects of secure system integration

- · Secure system integration of third-party hardware components

- Automated firmware generation supporting secure system execution

- Security aspects of reconfigurable designs

- Time-predictable system execution in open-hardware designs

- Performance analysis, timing analysis, and worst-case analysis supporting time-predictable system execution and/or communications in open-hardware designs

- Automated firmware generation supporting time-predictable execution

- Fault tolerance and execution in harsh conditions leveraging openhardware designs

- System architectures and methodologies supporting energy efficient/ performant system execution in open-hardware designs

- Hardware/software co-design, co-integration and co-verification of open-source processors, accelerators, and components

- Open architectures for reconfigurable platforms and open CAD tools

- Tools and analysis for open FPGAs and reconfigurable platforms

# WORKSHOP ON CHIPLET-BASED HETEROGENEOUS INTEGRATION AND CO-DESIGN (CHICO)

Time: 8:00 AM – 5:00 PM Session Type: Workshop Topic Area(s): EDA Room: 3003, 3rd Floor

**Organizer(s):** Yu Cao, University of Minnesota, Minneapolis, MN; Puneet Gupta, University of California, Los Angeles, CA

**Description:** Contemporary microelectronic design is facing tremendous challenges in memory bandwidth, processing speed and power consumption. Although recent advances in monolithic design (e.g. near-memory and in-memory computing) help relieve some issues, the scaling trend is still lagging behind the ever increasing demand of AI, HPC and other applications. In this context, technological innovations beyond a monolithic chip, such as 2.5D and 3D packaging at the macro and micro levels, are critical to enabling heterogeneous integration with various types of chiplets, and bringing significant performance and cost benefits for future systems. Such a paradigm shift further drives new innovations on chiplet IPs, heterogeneous architectures and system mapping.

This workshop is designed to be a forum that is highly interactive, timely and informative, on the related topics:

- Roadmap and technology perspectives of heterogeneous integration

- IP definition for chiplets

- Signaling interface cross chiplets

- Network topology for data movement

- Design solutions for power delivery

- Thermal management

- Testing in a heterogeneous system

- · High-level synthesis for the chiplet system

- Architectural innovations

- · Ecosystems of IPs and EDA tools

| Research<br>Sessions | Special<br>Session | Panel | Tutorial | Workshop;<br>Hands-on Labs | Exhibitor<br>Forum | DAC Pavilion Panel;<br>Analyst Review | TechTalk<br>SKYTalk | Keynotes and<br>Visionary Talks | Engineering<br>Track |

|----------------------|--------------------|-------|----------|----------------------------|--------------------|---------------------------------------|---------------------|---------------------------------|----------------------|

### Sunday, June 23, 2024

# GREAT: GEN-AI RESEARCH IN ELECTRONIC DESIGN, AUTOMATION, AND TEST

Time: 1:00PM – 5:00 PM Session Type: Workshop Topic Area(s): Design Room: 3004, 3rd Floor

**Organizer(s):** Ramesh Karri, New York University, New York City, NY; Siddharth Garg, New York University, New York City, NY; Jeyavijayan Rajendran, Texas A&M University, College Park, TX

**Description:** Large language models (LLMs) have been a significant breakthrough in artificial intelligence, demonstrating remarkable success in solving various real-world problems. These models, trained on vast amounts of text data, have shown an uncanny ability to generate human-like text, understand context, answer questions, and write code. They have been successfully deployed in numerous applications, including customer service, content creation, and language translation, to name a few. The versatility and robustness of LLMs have made them an invaluable tool in the AI toolkit, opening up avenues for exploration and innovation. Microsoft, Google, Meta, and Amazon have invested in generative AI technologies like LLMs.

One such avenue that has garnered attention is using LLMs in chip design. Digital chip design, a complex and intricate process, involves the creation of integrated circuits used in various electronic devices. LLMs are expected to aid designers during design and concept development, verification, validation, and security checks. For instance, Synopsys has recently developed an LLM-based framework to aid chip design and development.

With these revolutionary developments and interest from leading electronic design automation companies (Cadence, Synopsys, Siemens) and chip design companies (Intel, Nvidia, Qualcomm, IBM, etc.), there is an increasing need for a greater understanding of LLMs' roles in EDA. We are organizing this first "Workshop on Gen-AI for Chip Design", consisting of:

- (i) Introductory session on LLMs for chip design (1:00-1:30)

- (ii) Three-hour "Design a Chip in a Day" competition (e.g., RTL generation and testing) open to the EDA, AI, and Design community (students, academics, practitioners, hobbyists) (1:30-4:30)

- (iv) Closing session on the next steps (4:30-5:00) Together, these sessions will highlight the advances of LLMs for chip design, research adventures in academia, and provide hands-on experience for LLM-based chip design.

### HOW WILL AI DRIVE EDA AND IP GROWTH

Time: 5:00 PM - 6:00 PM Topic Area: Ai, EDA, IP Room: 3002, 3rd Floor

Author: Charles Shi, Needham & Company, LLC

**Description:** With the advent of generative AI, the landscape of the semiconductor industry is changing. AI is accelerating the in-sourcing of semiconductor design by systems companies. Vertical integration from silicon to systems is on the rise. One of the consequences of this changing landscape is that chip design appears to be capturing a greater piece of the pie in semiconductor value chain. This trend represents a major opportunity for the EDA and IP industry, who are the pick-and-shovel provider to the AI gold rush. In this presentation, we review the latest trends in semiconductors and explain why we think EDA and IP industry is the place to be in the AI super cycle.

Research Sessions Special Panel Session Tutorial Workshop; Hands-on Labs

Exhibitor Forum

DAC Pavilion Panel; Analyst Review TechTalk SKYTalk V

Keynotes and Visionary Talks

### Monday, June 24, 2024

### **KEYNOTE PRESENTATION WITH JIM KELLER**

Time: 8:45 AM – 9:45 AM Session Type: Keynote Room: 3007, 3rd Floor

**Description:** Jim Keller is CEO of Tenstorrent and a veteran hardware engineer. Prior to joining Tenstorrent, he served two years as Senior Vice President of Intel's Silicon Engineering Group. He has held roles as Tesla's Vice President of Autopilot and Low Voltage Hardware, Corporate Vice President and Chief Cores Architect at AMD, and Vice President of Engineering and Chief Architect at P.A. Semi, which was acquired by Apple Inc. Jim has led multiple successful silicon designs over the decades, from the DEC Alpha processors, to AMD K7/K8/ K12, HyperTransport and the AMD Zen family, the Apple A4/A5 processors, and Tesla's self-driving car chip.

### **A VIEW FROM WALL STREET**

Time: 10:15 AM – 11:00 AM Session Type: Analyst Presentation Topic Area(s): EDA Room: DAC Pavilion, Level 2 Exhibit Hall

**Description:** We will examine the financial performance and key business metrics of the EDA industry through 2023, as well as the material technical and market trends and requirements that have influenced EDA business performance and strategies. Among the trends, we will again examine the progression of semiconductor R&D spending and how the market value of the publicly held EDA companies has evolved. Lastly, we will provide our updated financial projections for the EDA industry for 2024 through 2026.

Speaker: Jay Vleeschouwer, Griffin Securities

# FLASH - AN OVERLOOKED TECHNOLOGY IN VLSI DESIGN

Time: 10:30 AM – 12:00 PM Session Type: Tutorial Topic Area(s): Design Room: 3002, 3rd Floor

**Description:** In the semiconductor industry, floating gate (flash) transistors have exclusively been used for non-volatile memory such as USB memory and solid-state drives (SSDs). This tutorial will present work on circuit design and design automation approaches demonstrating that flash can be used to design high-quality general-purpose VLSI ICs, both digital and analog. In particular, we will cover:

A) Flash-based realizations of both digital [2-9] and secure digital [1] ICs. These realizations have shown significantly improved power, delay and area compared to CMOS standard-cell based designs. The approaches in [2-7] use a PLA-based design flow. In contrast, [8-9] utilize a standard-cell based design approach augmented with flash cells, thereby leveraging many decades of EDA development in the standardcell based design flow. The approach of [1] provides significant security against foundry-based reverse engineering, without a penalty in power, delay or area compared to CMOS designs. In all these approaches, we have developed logic synthesis flows to automate the insertion of flash-based cells in the design.

B) Flash-based realizations of analog circuits such as low-dropout voltage regulators [10-11], Digital-to-Analog converters [13], FIR filters [12], and other DSP engines. Many benefits are availed by using flash-based designs for these [12-13] circuits, including reduced area, power, energy. In [10-11], flash-based design enables the use of the same design to achieve several LDO specifications, thereby resulting in a significant saving in manufacturing costs.

C) Flash-based mixed-signal designs such as convolutional neural network accelerators (both analog [14-16] and digital [17] variants), and other flash-based in-memory computing designs [18]. With flash-based mixed-signal current-mode CNN realizations [14-16], several common CNN architectures can be realized on the same die, resulting in 50X lower energy, and a latency improvement of 15X to 490,000X over [17], which is a state-of-the-art BNN.

A common theme of the above designs is that flash-based designs demonstrate several advantages over conventional CMOS designs, such as performance tunability, the ability to counteract circuit aging due to effects such as NBTI, the control of speed binning, and the ability to mitigate the effects of process variations. For secure designs, we show that if an adversary illegally gains possession of the IC, our approach can allow the functionality of a "kill switch", whereby the circuit operator can erase the flash transistors in the secure design, rendering it non-functional. We further demonstrate that scalability in the 3rd dimension can be leveraged for all these designs, using emerging 3D NAND and NOR flash technologies that are widely available for flash memory applications. Even though flash transistors do not scale to the feature sizes of traditional CMOS designs, we show that by using 3D flash fabrication techniques, a similar chip-level density (compared to traditional CMOS designs) in terms of transistors/area can be achieved.

Based on our findings, we posit that the programmability, robustness, stability, and maturity of flash give it a significant edge to CMOS in many ways, making it a practical alternative to CMOS in many applications.

**Presenters:** Sunil Khatri, Texas A&M University, College Station, TX; Sarma Vrudhula, Arizona State University, Tempe, AZ

| Research |  |

|----------|--|

| Sessions |  |

Special Session

Panel

Workshop; Hands-on Labs

Tutorial

Exhibitor DAC Pavilion Panel; Forum Analyst Review

on Panel; TechTalk Review SKYTalk

lk Keynotes and Ik Visionary Talks

# GDSFACTORY: AN OPEN SOURCE PLATFORM FOR END-TO-END CHIP DESIGN, VERIFICATION AND VALIDATION

Time: 10:30 AM – 12:00 PM Session Type: Tutorial Topic Area(s): EDA Room: 3003, 3rd Floor

**Description:** For efficient design, verification and validation of integrated circuits and components it is important to have an easy to customize and extend workflow. Python has become the standard programming language for machine learning, scientific computing and engineering.

Gdsfactory is a python library to build chips (Photonics, Analog, Quantum, MEMs, ...) that provides you a common syntax for design (KLayout, Ansys, tidy3d, MEEP, MPB, DEVSIM, SAX, ...), verification (Klayout DRC, LVS, netlist extraction, connectivity checks, fabrication models) and validation (JAX neural network model extraction, pandas, SQL database).

In this tutorial we will cover the gdsfactory design automation tool. Gdsfactory provides you an end to end workflow that combines layout, verification and validation using an extensible, open source, python driven flow for turning your chip designs into validated products.

$https://gdsfactory.github.io/gdsfactory-photonics-training/notebooks/10\_layout\_full.html$

**Presenters:** Joaquin Matres, Helge Gehring, Google, Mountain View, CA; Simon Bilodeau, Princeton University, Princeton, NJ; Niko Savola, Aalto University, Espoo, Finland; Troy Tamas, Rockley Photonics, Pasadena, CA

# HIGH PERFORMANCE COMPUTING USING SUPERCONDUCTOR ELECTRONICS

Time: 10:30 AM – 12:00 PM Session Type: Tutorial Topic Area(s): Design Room: 3001, 3rd Floor

**Description:** This half-day tutorial aims to impart a comprehensive understanding of the theory and application of superconductor electronics, spanning from the foundational principles of superconductivity to the operational intricacies of superconductor logic cells and digital circuits. The tutorial will explore diverse applications, ranging from neuromorphic computing and signal processing to homomorphic computing and quantum computing.

**Presenters:** Massoud Pedram, Sasah Razmkhah, University of Southern California, Los Angeles, CA; D. Scott Holmes, IEEE IRDS, Washington, DC; Eby Friedman, University of Rochester, Rochester, NY

# EXPLORE CONCEPTS OF STA THRU INSIGHTFUL CRAFTSMANSHIP

Time: 10:30 AM – 12:00 PM Session Type: Engineering Track Topic Area(s): Back-End Design Room: 2008, 2nd Floor

Session Chairs: Lakshmanan Balasubramanian, Texas Instruments (India) Pvt. Ltd., IEEE

**Description:** TBD. Dusamusda con pro oditatur molorum quam et audio. Ut aut de pore eicipis inti ut et ent quae vellit erchitatur, qui ant, quid est, et aut labor aut aut aliqui berument magnisitas simentius aut ilia sitatib usdaernata ipsandae prorpor acea por sunt exerepudae estiorem repro ommo eos dolorerio. Itate prem voluptae et alit accabor epelitatur? Qui con nonsequas sandenist a sinus mo eate volorest reped etur, omnim eum restio. Ebisciatet pel inusti berendae. Lendit qui dolo eos evellorero estis volorum am et velit lamet atem dia vitatur mint que omnimint facest elis entin everitatem estrum imin cum nis evendae cone solorem. Ut eatur alicipsum quis imagnis magni ratiis auda consequi quiam nimpores

TSV KOZ Separation 3DIC P&R Area Optimization Methodology Considering Device Impact by TSV

Yongjin Hong, Ki-Ok Kim, Mijeong Lim, Jun Seomun Byunghyun Lee, Sangyun Kim, Samsung Electronics, Seoul, South Korea;

- ML Based PPA Push using DRV Prediction

Jungho Kim, Kyoungsun Cho, Sunghoon Kim, Mintae Lee, Wook Kim,

Ki-Ok Kim, Sangyun Kim, Samsung, Seoul, South Korea;

- Model Margining Algorithm for High Performance SOC closure Subhadeep Aich, Tejas Salunkhe, Siddharth Sarin, Gaurav Patil, Texas Instruments, Bengaluru, India;

- Pruning Netlist: A Smarter Approach to Efficient and Reliable Circuit Characterization Harsh Garg, Pawan Verma, Saurabh Srivastava, Anil Dwivedi, Fillaud Matthieu, Siemens, Grenoble, France;

- Clock Parameter Tuning with an Intelligent Adaptive Learning to Improve Performance and Power of Multisource Clock Tree Synthesis

Divyarajsinh Vaghela, Jagadeesh Gnanasekaran, Gaurav Bhatia, Intel, Karnataka, India;

An Effective Hierarchical STA Solution for Closing Large SoC Design

Shourya Shukla, Sainarayanan Suryanarayanan, Marvell, Bengaluru, India; Sushant Hajare, Marvell, Jaipur, India; Harshit Jaiswal, Sharath AC, Cadence Design Systems, Inc., Bengaluru, India; Nitin Jain, Cadence Design Systems, Inc., Montbonnot-Saint-Martin, France

Research Sessions Special Panel Session Tutorial

Workshop; Exhibitor Hands-on Labs Forum DAC Pavilion Panel; Analyst Review TechTalk Keynotes and SKYTalk Visionary Talks

# AI CO-PILOT: EXPLORING THE AI FRONTIER IN CHIP DESIGN

Time: 10:30 AM – 12:00 PM Session Type: Engineering Track Topic Area(s): Front-End Design Room: 2010, 2nd Floor

**Organizers:** Moshe Zalcberg, Veriest Solutions Ltd., Petach Tikva, Israel

Moderator: Serge Leef, Microsoft, Camas, WA

**Description:** Generative AI is everywhere, but it's still making its first steps in Chip Design. In this session, we'll invite representative from the design community to review the challenges and present working solutions on using AI for front-end chip design, with an emphasis in sharing "how-to" ideas.

**Presenters:** Sid Dhodhi, NVIDIA, Santa Clara, CA; Amber Telfer, Microsoft, Hillsboro, OR; Priyanka Mathikshara, Voltai, Stanford, CA

# CHERISHED MEMORIES - EXPLORING THE POWER OF INNOVATIVE MEMORY ARCHITECTURES FOR AI APPLICATIONS

Time: 10:30 AM – 12:00 PM Session Type: Engineering Track Topic Area(s): IP Room: 2012, 2nd Floor

Organizers: Moshe Zalcberg, Veriest Solutions Ltd.

Moderator: Raul Camposano, Silicon Catalyst, Santa Clara, CA

**Description:** With all the discussion about Moore's Law, one thing is for sure: Memories aren't scaling as much as logic. On the other hand, Al applications, so popular these days, require increasing amount of memory. Add to that the need to extend the use of available fabs, and you get a great reason to explore new memory paradigms.

In this session we'll explore cutting-edge technologies transforming the landscape of memory design. The expert speakers will share real-world applications in Al, machine learning, and edge computing, exploring new technologies and optimization strategies.

**Presenters:** Andreas Burg, RAAM Technologies, Zurich, Switzerland; Gideon Intrater, Weebit Nano, San Francisco, CA; Sushil Sudam Sakhare, Veevx Inc, Mesa, India

# SECURE COLLABORATION ACROSS ENTERPRISES ON THE CLOUD

Time: 10:30am – 11:00am Session Type: Exhibitor Forum Topic: IP

Room: Exhibitor Forum, Level 1 Exhibit Hall

Description: Modern SoCs require the integration of IP and tools from multiple vendors. Chip designers often must work with their IP vendors, tool vendors, and design service providers. This collaboration often requires enterprises to onboard third parties into their network to jointly work on a solution, requiring security exceptions. By leveraging the cloud as a secure independent collaboration platform, customers no longer need to make compromises with security to onboard third parties. The Microsoft Azure Modeling and Simulation Workbench makes it easy for customers to bring up a secure design environment and invite third parties to collaborate while keeping them isolated to the workbench.

Presenters: Prashant Varshney, Microsoft

### ULTRA-FAST VARIATION CHARACTERIZATION FOR EMBEDDED MEMORIES AND IP BLOCKS

Time: 11:15 AM – 11:45 AM Session Type: Exhibitor Forum Room: Exhibitor Forum, Level 1 Exhibit Hall

**Description:** Process variation library models in the Liberty Variation Format (LVF) have become commonplace in timing signoff for standard cells, yet the embedded memories that comprise most of the chip area still employ library modeling methodologies from several technology generations ago. The main challenge is the greatly increased amount of simulation required to extract meaningful LVF data compared to nominal timing characterization.

It is known that the effect of random process variation is local to a small portion of the circuit. LVF characterization methods based on full-macro or critical-path simulation observe these effects at a global or near-global scale. As a result, they cannot fully utilize the simulation power and causes inefficiency. We believe a good methodology combining strategically partitioning the design and localized OCV models can greatly improve the efficiency of LVF characterization, without compromising accuracy.

This presentation unveils the key technologies behind Liberal-Mem, the memory characterization system from Empyrean, with a highly efficient solution to embedded memory characterization, especially to LVF extraction.

Presenters: Danny Li, Ken Tseng, Empyrean Technology

Workshop; Hands-on Labs

Tutorial

Exhibitor DAC Pavilion Panel; Forum Analyst Review

# BEST OF BOTH WORLDS: BRIDGING THE GAPS IN ENGINEERING SOFTWARE FOR SEMICONDUCTORS AND SYSTEMS

Time: 11:15 AM – 12:00 PM Session Type: Pavilion Panel Room: DAC Pavilion, Level 2 Exhibit Hall

Moderator: Jay Vleeschouwer, Griffin Securities

**Description:** This panel will explore, with leading software companies, a phenomenon that has long been anticipated: the business, market and technical convergences of the two halves of Engineering Software (EDA and "industrial" software). These convergences are increasingly evident in the companies' product and acquisition strategies.

**Panelists:** Tom Beckley, Cadence Design Systems, Inc.; Philippe Laufer, Dassault Systemes; Niels Fache, Keysight; Shankar Krishnamoorthy, Synopsys; Tony Hemmelgam, Siemens; Paul Sagar, PTC

### ENABLING A NEW ERA OF SOFTWARE SHIFT LEFT WITH VELOCE CS

Time: 12:00 PM – 12:30 PM Session Type: Exhibitor Forum Room: Exhibitor Forum, Level 1 Exhibit Hall

### Speaker: Vijay Chobisa, Siemens

**Description:** As software defined products become the norm and software workloads impact every aspect of system architecture and implementation, we need ways to include software in every aspect of the design from early architecture exploration, through logic design, and into integration and validation. This places new demands on systems designers, creates new verification challenges, and at the same time opens opportunities for design teams to begin software design long before silicon availability.

In this presentation we will explore the changing face of design in a software defined world, how software shift lest can accelerate product development while reducing risk, and how the unique capabilities offered by the new Siemens EDA Veloce CS platform makes software shift left available to all design teams.

# CHIPS FOR AMERICA AND SUSTAINED U.S. LEADERSHIP: A VISION FOR INNOVATION THROUGH THE NATIONAL SEMICONDUCTOR TECHNOLOGY CENTER (NSTC)

Time: 1:00pm – 1:45pm Session Type: SKYTalk Topic: EDA Room: DAC Pavilion, Level 2 Exhibit Hall

Description: The semiconductor industry has always moved fast, but changes in the industry over recent years have been historic. We will discuss a variety of challenges in the ecosystem, and how the NSTC can unite the community to address those challenges. Some of these are technical - logic, mixed signal, memory, photonics, design / co-design, and architecture all need new breakthroughs to continue to advance the state of technology. Others are ecosystem challenges. Access to design tools, IP, and collaboration environments, as well as increasing use of Al in the design and verification flow will all transform the way that the industry does its work. Access to advanced R&D facilities and leadingedge shuttles can accelerate the pace of research. The traditional venture model has been mismatched with hardware investments for decades, and this has been a drag on innovation, but there are new ideas for how this can work better. In closing, we will provide updates on the priorities for this year and show how the NSTC can change the long-term trajectory for innovation.

Presenters: Jay Lewis, National Semiconductor Technology Center

Research Sessions Special Panel Session Workshop; Hands-on Labs

Tutorial

Exhibitor DAC Pav Forum Analys

DAC Pavilion Panel; Analyst Review

TechTalk Keynotes and SKYTalk Visionary Talks

# AUTOMATED CO-DESIGN OF COMPLEX SYSTEMS: FROM AUTONOMY TO FUTURE **MOBILITY SYSTEMS**

Time: 1:30 PM - 3:00 PM Session Type: Tutorial Topic Area(s): Design Room: 3003. 3rd Floor

**Description:** The contemporary era struggles with the intricate challenge of designing "complex systems". These systems are characterized by intricate webs of interactions that interlace their components, giving rise to multifaceted complexities, springing from at least two sources.

First, the co-design of complex systems (e.g., a large network of cyber-physical systems) demands the simultaneous selection of components arising from heterogeneous natures (e.g., hardware vs. software parts), while satisfying system constraints and accounting for multiple objectives.

Second, different components are interconnected through interactions, and their design cannot be decoupled (e.g., within a mobility system). Navigating this complexity necessitates innovative approaches, and this tutorial responds to this imperative by focusing on a monotone theory of co-design. Our exploration extends from the design of individual platforms, such as autonomous vehicles, to the orchestration of entire mobility systems built upon such platforms.